‘Skyscraper’ Chips Promise Powerful Computing

Boost !!

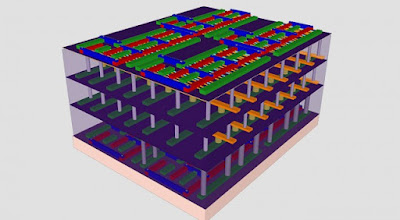

A team of researchers led by Stanford’s Mohamed M. Sabry Aly, Subhasish Mitra, and H.-S. Philip Wong want to put a “skyscraper” of computer chips in your next PC. The idea is to stack application processors, memory modules, and other components one on top of the other in “a revolutionary new high-rise architecture for computing,”according to the Stanford News Service.

Such an “electronic super-device” using the team’s Nano-Engineered Computing Systems Technology, or N3XT, could power a computer which combines “higher speed with lower energy use [to] outperform conventional approaches by a factor of a thousand,” Wong told Stanford’s news journal.

Stacking chips has long been seen as a viable path towards building a more efficient, powerful computing architecture than the current template, which lays out and connects components on a flat board, like “single-story structures in a suburb,” as the researchers put it. But building a “skyscraper” of chips has thus far proven difficult using silicon-based integrated circuits (ICs), which are tough to connect reliably in a stacked structure.

Sabry Aly, Mitra, Wong, and their colleagues believe they’ve figured out a way around such issues using “new nano-materials” to construct stacked computer chips in place of traditional silicon ICs. Dubbed Nano-Engineered Computing Systems Technology, or N3XT, the process involves building carbon nanotube transistors (CNTs) in a stacked arrangement. The upshot is that instead of the relatively limited number of wires connected stacked silicon chips, a N3XT device could employ “millions of electronic elevators that can move more data over shorter distances that traditional wire, using less energy,” per the researchers.

Instead of adding traditional wires to connect stacked chips in a N3XT system, communication between components is built in during the actual process of fabrication. Since CNTs can be created at much lower temperatures than silicon-based transistors, it’s possible to build components on top of each other, like a processor on a memory module, while maintaining the integrity of those tiny “electronic elevators,” the researchers noted. Silicon ICs, on the other hand, have to be fabricated separately from each other and then stacked in “3D” arrangements later, which precludes integrating those interconnects from the get-go.

The team is also incorporating cooling in its N3XT devices, just as traditional two-dimensional computing architectures must have their thermals kept in check to prevent overheating. Stanford mechanical engineers Kenneth Goodson and Mehdi Asheghi are leading the effort to “incorporate thermal cooling layers” in the stacked chips, according to Stanford News Service.

The team has published its findings in a recent special issue of IEEE Computer.

One major roadblock to the adoption of N3XT or chip-stacking technologies like it? The global semiconductor industry is massively invested in silicon-based process technology, the researchers noted.

“Shifting electronics from a low-rise to a high-rise architecture will demand huge investments from industry,” they were quoted as saying.

Still, the incentive to do so is compelling, said N3XT article co-author Chris Re, a Stanford computer scientist and MacArthur Foundation “genius grant” winner.

“There are huge volumes of data that sit within our reach and are relevant to some of society’s most pressing problems from health care to climate change, but we lack the computational horsepower to bring this data to light and use it,” Re told Stanford News Service. “As we all hope in the N3XT project, we may have to boost horsepower to solve some of these pressing challenges.”

Comments

Post a Comment